기호 및 약어 설명

CVD : Chemical Vapor Deposition

FET : Field Effect Transistor

GaN : Gallium Nitride

PCB : Printed Circuit Board

TIM : Thermal Interface material

FR4 : Flame Retardant 4

1. 서 론

UN에 따르면 현재 기준으로 전 세계 130개국 이상에서 2050년까지 탄소중립 달성을 공표하였다1). 이에 각국 정부는 온실가스 배출을 최소화하면서 경제적 파급효과를 최소화해야 하는 당면과제에 직면해 있다. 우리나라 정부는 에너지 관련 모든 부문, 에너지 공급, 산업, 수송, 건물, 폐기물 등을 포함한 ‘2050 탄소중립 추진전략’을 발표하였고, 석탄발전과 원자력 발전을 대폭 줄여나가면서 신재생에너지를 이용한 발전을 지속해서 확충한다는 ‘제9차 전력수급기본계획’을 발표하였다2). 전력거래소에 따르면 2021년 기준 국내 전체 신재생에너지 발전설비 중 태양광 발전용량은 14.6 GW로 71% 비중을 차지한다. 이러한 추세에 따라 고효율/고전력 밀도를 가지는 태양광발전 전력변환장치에 대한 시장이 급속히 확대되고 있다3).

전 세계적으로 반도체 소자 영역에서 전기를 절약하기 위하여 고효율, 친환경 파워디바이스에 개발이 활발히 진행 중이다. 파워디바이스는 신호 및 정보를 처리, 저장하는 시스템 반도체나 메모리 반도체와 달리 전기에너지의 변환/제어 처리를 수행하는 반도체 소자로서 전기를 처리하는 모든 전기전자기기(스마트 그리드, 가전, 스마트폰, 자동차 등)에 사용되는데 주로 전력변환(AC → DC, DC → AC), 전력변압(감압, 승압), 전력안정, 전력효율 최적화(분배, 제어) 등에 사용된다4). 밴드갭이 넓은 화합물 반도체인 GaN (Gallium Nitride)은 실리콘 소재 대비 우수한 물성으로 차세대 파워디바이스에서 요구되는 고내압 및 고전류 구동이 가능한 장점이 있어 최근 들어 태양광발전 전력변환장치에 적용 및 응용 연구가 진행되고 있다5). GaN 기반의 소자는 월등히 높은 출력과 고효율의 장점이 있지만, 운용 시 많은 발열이 수반되므로 성능 및 내구성을 유지하기 위해 소자 설계 및 패키징 기술과 함께 반드시 우수한 방열성능이 확보되어야 한다6). 본 연구에서는 GaN 기반 FET (Field Effect Transistor)의 방열성능을 향상시키기 위해 다양한 PCB (Printed Circuit Board)의 방열구조를 비교하고 최적 방열구조를 제시하고자 한다.

최근 전자기기의 고성능 및 소형화 경향에 따라 제한된 구조에서 효과적인 방열 효과를 달성하기 위한 많은 연구가 진행되었다. Lee et al. (2010)7)은 LED 패키지에서 발생하는 열을 효과적으로 방열하기 위해 바이어 홀(Via-Hole)을 적용한 방열구조를 연구한 바 있으며, 수치해석을 이용하여 0.6 mm의 직경을 갖는 바이어 홀을 적용하였을 때 가장 좋은 방열 효과가 보이는 것을 확인하였다. Yoon et al. (2016)8)은 항공전자장비에 바이어 홀을 적용한 경우 방열 특성에 미치는 영향을 수치해석을 이용하여 분석하였으며, 바이어 홀의 크기가 작고 많을수록, 바이어 홀을 둘러싼 구리의 두께가 두꺼울수록 열저항 값이 낮아지는 것을 확인하였다. Kim et al. (2016)6)는 GaN 소자 패키지의 방열효율 향상을 위해 열전도도가 높은 CVD (Chemical Vapor Deposition) diamond 소재를 적용하는 수치해석 연구를 수행하여 방열효과가 10% 이상 향상되는 것을 확인하였다. Jeong et al. (2019)9)은 바이어 홀에 Cap 도금을 적용하여 기존 금속기반 PCB를 FR4 (Flame Retardant 4) 기반 PCB로 대체할 수 있는 가능성을 확인하였다. Han et al. (2021)3)은 GaN 소자 기반 태양광 인버터의 방열 설계 및 개발을 수행한 바 있으며, 바이어 홀 설계 및 낮은 열저항의 절연재를 통해 우수한 방열 성능을 확보하여 한 시간 동안 동작 시 온도변화량이 35.6℃로 설계 수치를 추종하는 것을 확인하였다.

GaN-FET에서 발생하는 열은 전도를 통해 PCB에 전달되고, PCB와 GaN-FET 표면에서 대류를 통해 외부 공기로 배출된다. GaN-FET의 운용 시 고발열에 대응하기 위해 금속 소재 기반 PCB의 적용이 필요하지만 본 연구에서는 태양광발전 단가 최소화를 위해 GaN-FET이 장착되는 PCB의 소재로 FR4를 채택하였다. 낮은 열전도도를 가지는 FR4 기반 PCB를 GaN-FET이 적용된 전력변환장치에 적용하기 위해서는 두께방향의 열전도 향상을 위한 바이어 홀과 제한된 공간에서 전열면적을 향상시키는 방열판의 적용이 필수적이며, 수치해석을 통한 방열특성 분석이 필요하다. 본 연구에서는 수치해석을 이용하여 3 kW급 태양광발전 시스템에 적용할 수 있는 전력변환장치용 GaN-FET의 효과적인 방열을 위해 다양한 방열구조로 이루어진 FR4 (Flame Retardant 4) 소재를 적용한 PCB의 방열특성을 분석하였다. 본 연구에서는 PCB에 적용된 바이어 홀의 대기 노출 유무에 따른 방열효과를 확인하기 위한 방열구조 2종과 PCB의 상향 냉각과 상하향 냉각효과를 비교하기 위한 방열구조 2종의 방열특성을 비정상상태 열해석이 가능한 ANSYS Transient-Thermal Analysis 프로그램을 이용하여 분석하였다.

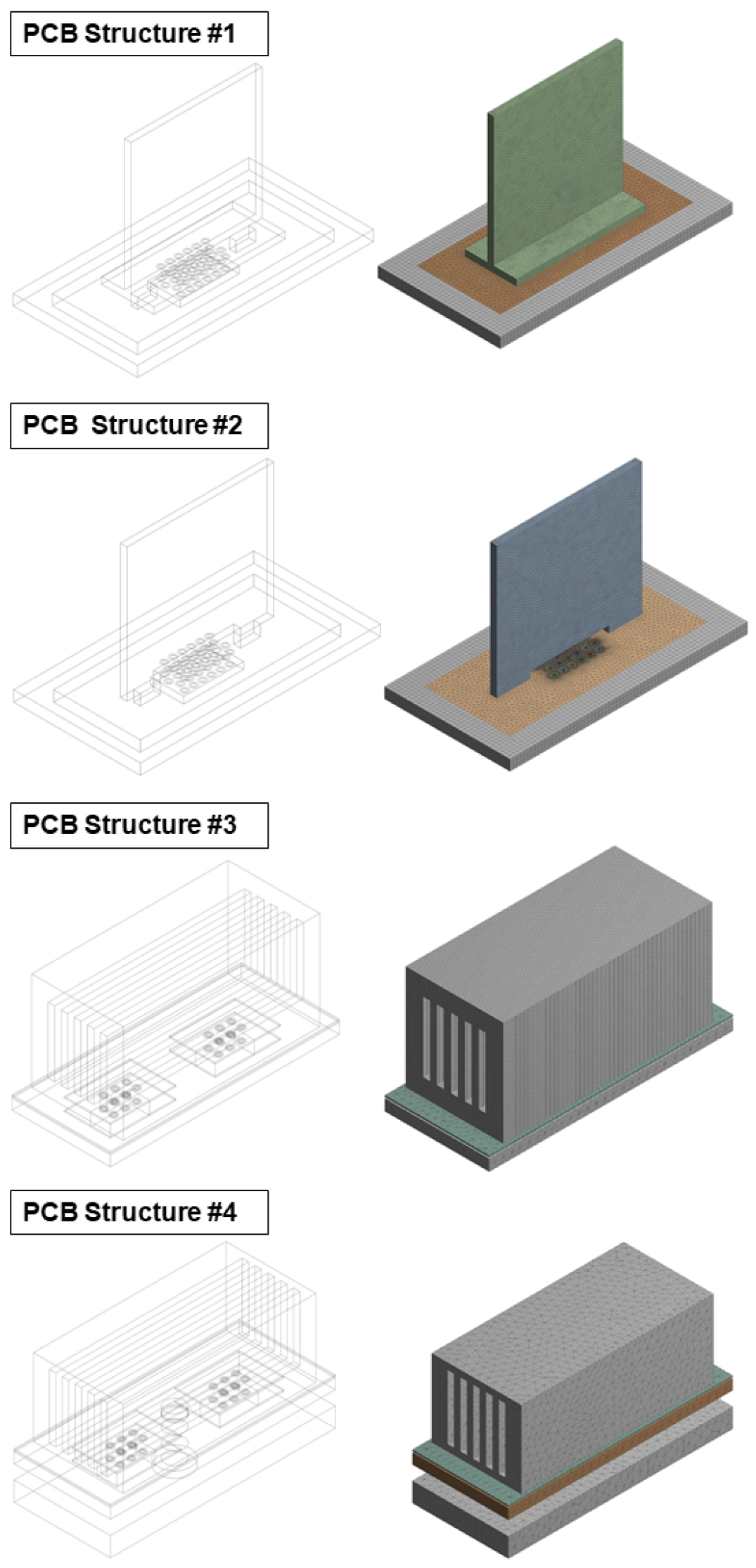

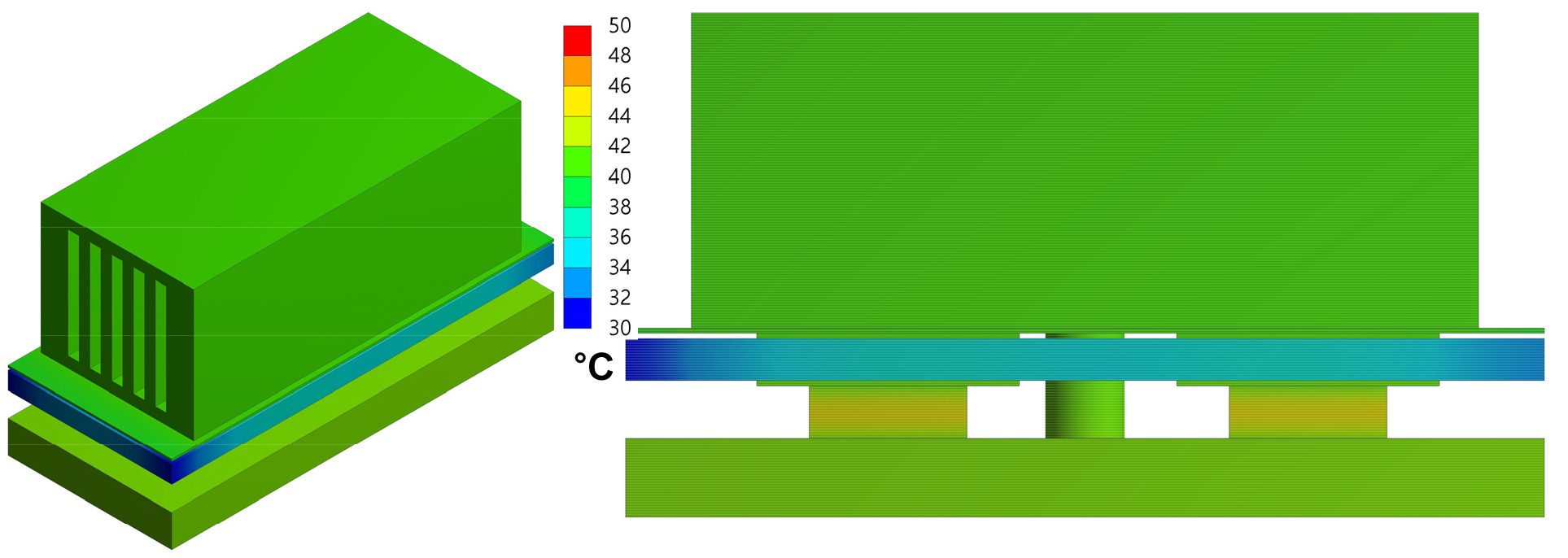

2. 수치해석 방법

2.1 수치해석 형상과 격자

본 연구에서는 수치해석을 위해 실제 GaN-FET이 적용된 복잡한 형상의 PCB 패키지에서 일부분을 발췌한 형상을 적용하였다. Fig. 1에서 방열구조 1과 2는 바이어 홀의 외기 노출 유무에 따른 PCB의 방열특성을 확인하기 위해 수치해석에 적용된 방열구조 2종의 형상과 격자를 나타낸 것이다10). 두께 1.6 mm의 PCB 양면에는 바이어 홀의 단면 형태로 타공된 0.035 mm의 동박이 부착되어 있으며, PCB 하부면의 동박에 1개의 GaN-FET이 각각 부착되어 있다. 방열구조 1과 2에 적용된 GaN-FET의 가로, 세로, 그리고 높이는 각각 9 mm, 5 mm, 그리고 1 mm 이다. 24개로 구성된 PCB 내부 바이어 홀의 내경은 0.6 mm이고 0.4 mm의 두께로 금이 코팅되어 있다. 방열구조 1의 경우 방열판과 바이어 홀이 직접 접촉하고 있는 형상이며, 방열구조 2의 경우 바이어 홀이 대기 중에 노출된 형상이다. 각 방열판의 두께는 1 mm이고, 높이는 20 mm이다. Fig. 1에서 방열구조 3과 4는 PCB의 상향 냉각과 하향 냉각효과를 비교하기 위해 수치해석에 적용된 방열구조 2종의 형상과 격자를 나타낸 것이다11). PCB 두께는 Fig. 1의 경우와 같으며, TIM (Thermal Interface Material)은 0.2 mm, PCB 양면에 부착된 동박의 두께는 0.2 mm이다. PCB 하부면의 동박에는 GaN-FET 2개가 각각 부착되어 있다. 방열구조 1과 2의 경우와 달리 GaN-FET의 가로, 세로, 그리고 높이는 각각 6 mm, 3 mm, 그리고 2 mm이다. 각 GaN-FET당 6개로 구성된 PCB 내부 바이어 홀의 내경과 코팅 두께는 Fig. 1의 경우와 같으며, 코팅 소재로 구리가 적용되었다. 방열구조 3은 PCB 상부에 직사각형 형태의 홀 5개가 타공되어 있는 방열판이 부착된 형태이며, 방열구조 4는 PCB 상부 방열판과 함께 PCB와 알루미늄 볼트로 체결된 두께 3 mm의 알루미늄 판을 추가로 GaN-FET 하부에 부착시킨 형태이다. 방열구조 4의 PCB 상부 방열판은 기존 PCB 패키지에 적용할 수 있도록 알루미늄 판의 두께만큼 방열판의 높이를 낮게 하였다. 방열구조 1 ~ 4의 격자수는 각각 1,177,909개, 1,578,061개, 362,302개, 그리고 190,453개이다.

2.2 수치해석에 적용된 소재

PCB 방열해석에 적용된 소재의 열역학적 물성을 Table 1에 나타내었다. 모든 방열구조의 방열판 소재는 알루미늄을 적용하였다. 방열구조 1과 2에는 TIM이 고려되지 않았고, 방열구조 3과 4에는 고려되었다. 방열구조 1과 2의 바이어 홀의 코팅 소재로 금이 적용되었으며, 방열구조 3과 4에는 구리가 적용되었다. 바이어 홀에 FR4-PCB, GaN-FET, 그리고 TIM의 열역학적 물성은 실제 시스템 개발에 활용된 소재의 수치를 적용하였으며, 구리, 금, 그리고 알루미늄의 열역학적 물성은 ANSYS Engineering Data에서 제공하는 수치를 적용하였다.

Table 1

Properties of materials for thermal analysis

2.3 수치해석 모델

본 연구에서는 소재의 비정상상태 열해석을 위해 ANSYS Transient-Thermal Analysis 프로그램을 활용하였다. ANSYS Transient-Thermal Analysis에서 비정상상태 열해석의 지배방정식은 아래 식(1)에 나타내었다12).

여기서 k는 소재의 열전도계수(W/mK), t는 시간, T는 소재의 온도(K), q는 대류 및 복사에 의한 열전달률 또는 내부 발열량(W), ρ는 소재의 밀도(kg/m3), 그리고 c는 소재의 비열을 나타낸다. 식(1)의 우변은 비정상상태를 나타낸다.

2.4 수치해석 조건

본 연구에서는 PCB 방열해석을 위해 초기조건으로 PCB의 온도를 25℃로 적용하였고 경계조건으로 외기온도는 25℃와 대류열전달 계수 10 W/m2K를 적용하였으며, 복사열전달은 고려하지 않았다. 방열구조 1의 바이어 홀은 외기에 노출되어 있는 상태로 외부 경계조건 설정을 통해 대류 열전달의 고려하였고, PCB 내부에 있는 방열구조 2 ~ 4의 바이어 홀은 내부 공기가 거의 없는 상태로 공기의 열전도만 고려하여 열해석을 진행하였다. 온도가 급격히 변화하는 구간을 촘촘히 해석하기 위해 초기 time step과 최소 time step을 0.001초로 하였고, 최대 time step은 2초로 하였다. PCB의 열적평형이 이루어져서 온도 변화율이 0이 될 때까지 충분히 해석하기 위해 step end time은 4,000초로 적용하였다.

3. 결과 및 토의

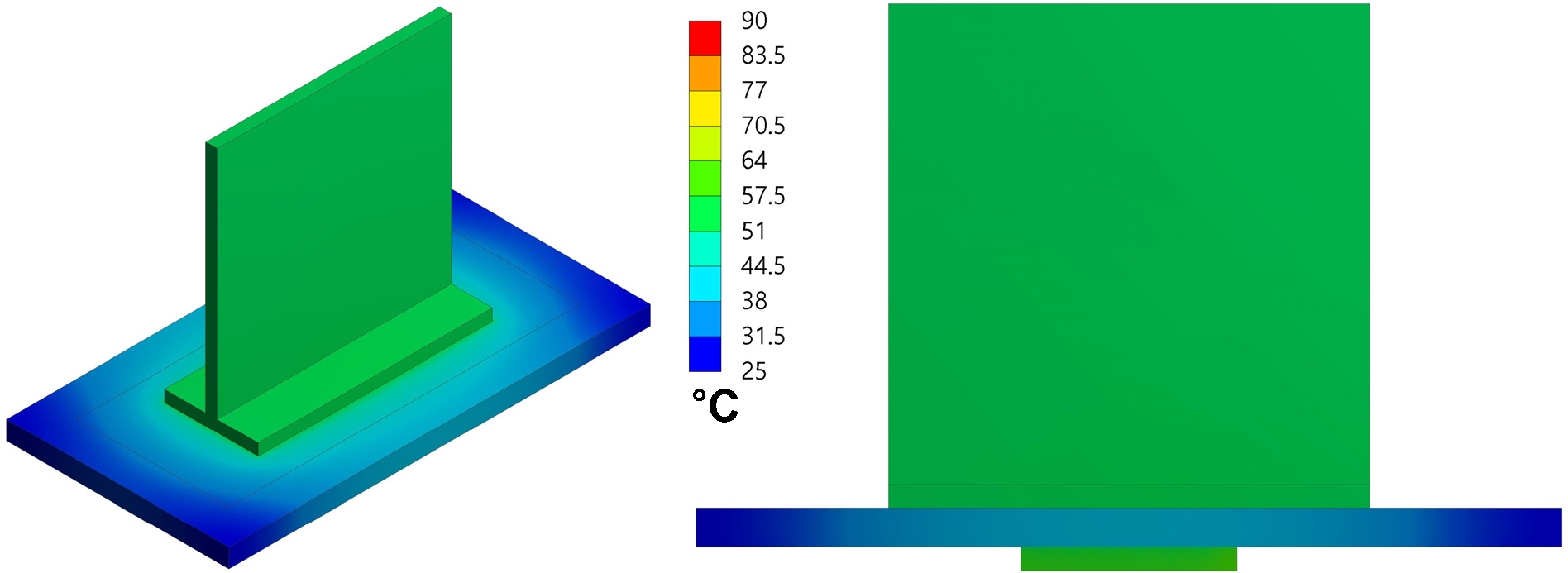

Figs. 2와 3은 해석 시간이 4,000초일 때 방열구조 1과 2의 표면온도 분포를 나타낸 것이다. GaN-FET 표면온도는 방열구조 1보다 방열구조 2에서 높게 나타나고 방열판의 표면온도는 방열구조 1에서 방열구조 2보다 높게 나타나는 것을 확인할 수 있다. 방열구조 2는 GaN-FET에서 발생하는 열의 대부분이 전도를 통해 바이어 홀에 전달되어 자연대류의 형태로 주위로 방열되고 일부 열은 PCB로 전달되어 방열판을 통해 주위로 방열되는 방식으로 방열구조 1이 채택하고 있는 바이어 홀과 방열판이 접촉하여 빠른 전도를 통해 GaN-FET에서 발생하는 열이 방열판으로 전달되는 방식보다 접촉면적이 작아 방열경로가 좁게 형성되므로 열전달 효율이 떨어지는 것으로 판단된다13). 또한, 방열구조 2의 바이어 홀이 외기 노출되어 있음에도 불구하고 방열구조 2의 전열면적은 1,010 mm2으로 방열구조 1의 1,056 mm2보다 다소 작게 형성되므로 방열구조 1의 설계가 방열구조 2보다 효과적인 방열을 위해 유리하다고 판단된다. 따라서, 본 연구를 통해 열전도도가 낮은 PCB에 바이어 홀을 적용할 경우 발열체와 방열판이 바이어 홀에 직접 접촉하도록 구성해야 방열효과를 극대화할 수 있는 것으로 결론 내릴 수 있으며, 향후 운용 시 고발열이 예상되는 시스템의 필수 방열설계로 활용이 가능하다.

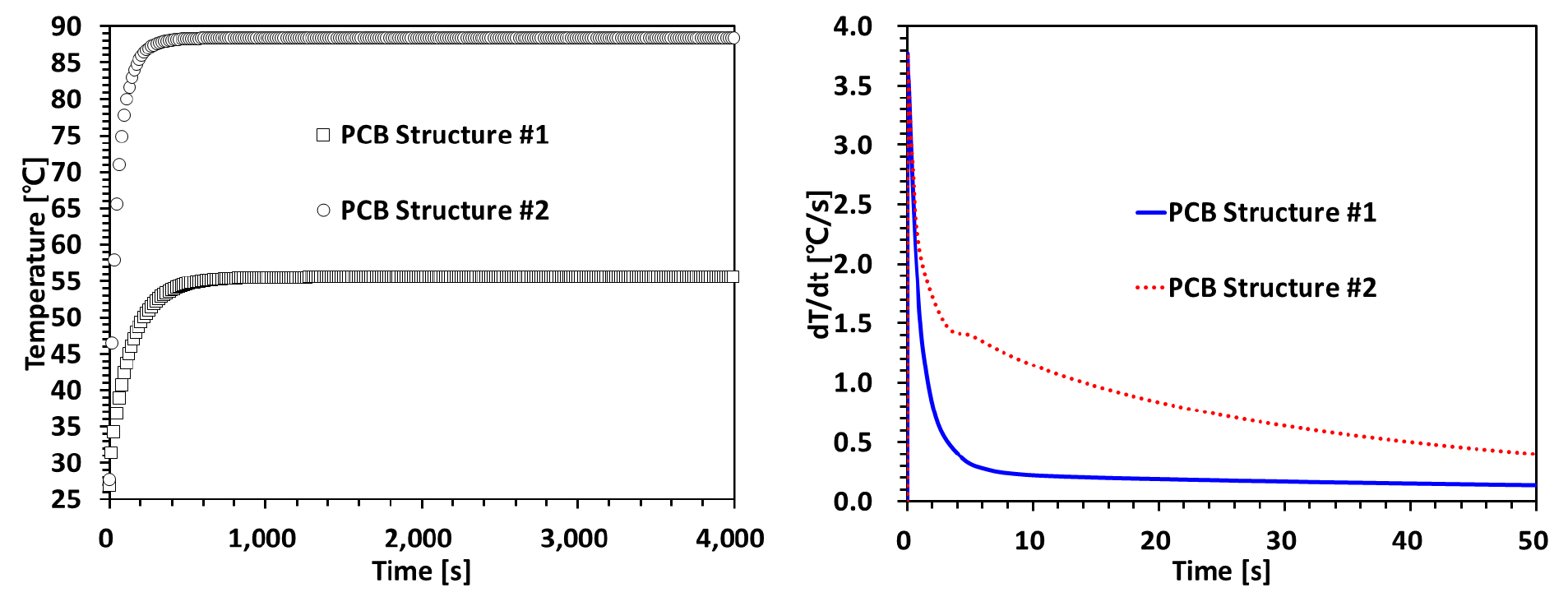

Fig. 4는 방열구조 1과 2의 시간에 따른 GaN-FET의 최대 온도와 최대 온도 변화율을 나타낸 것이다. 두 경우 모두에서 해석 시간이 300초에 도달하기 전 GaN-FET의 최대 온도가 안정되는 것을 확인할 수 있다. GaN-FET의 최대 온도는 방열구조 1에서 약 55 ℃이고 방열구조 2에서 약 88 ℃로 나타났다. 이는 앞서 설명한 바대로 방열구조 1의 방열방식이 방열구조 2보다 유리하기 때문으로 판단된다. Fig. 4에서 방열구조 1과 2 모두 해석 시작 후 최대 온도 변화율이 급격히 상승하여 최대 수치인 3.78 ℃/s에 도달하는 것을 확인할 수 있다. 방열구조 2에서는 GaN-FET의 최대 온도 변화율이 최대 수치 도달 후 방열구조 1의 경우보다 완만히 감소하는 것을 확인할 수 있는데 실제 전력변환장치 운용 시 급격한 발열에 대비하는 측면에서 방열구조 1이 방열구조 2보다 더 유리한 것으로 보인다.

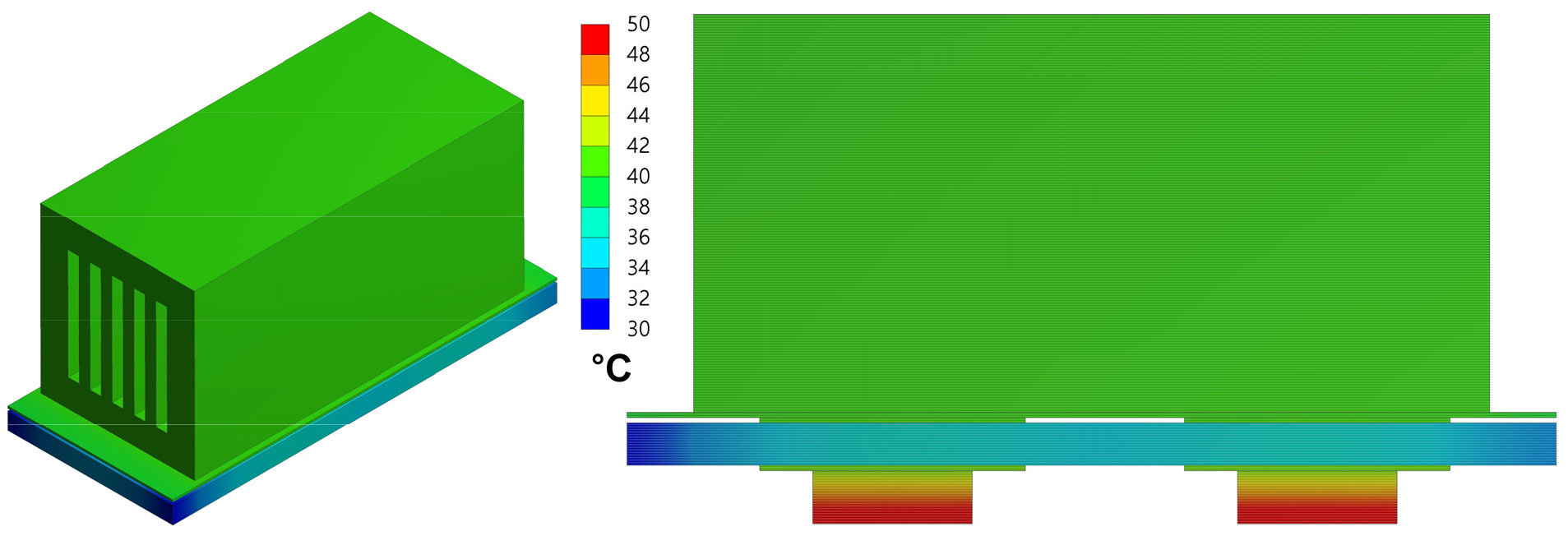

Figs. 5와 6은 해석 시간이 4,000초일 때 방열구조 3과 4의 표면온도 분포를 나타낸 것이다. GaN-FET의 표면온도는 방열구조 4보다 3에서 높게 나타났고, 방열판의 표면온도는 방열구조 3보다 4에서 비교적 높게 나타났다. 방열구조 4의 경우 GaN-FET 하부에 부착된 알루미늄 판으로 전도를 통해 GaN-FET에서 발생하는 열이 전달되어 신속히 주위로 방열되기 때문으로 방열구조 3의 경우보다 GaN-FET의 온도가 낮게 나타난 것으로 판단된다. 또한, 알루미늄 볼트를 통해 방열경로가 형성되어 PCB 하부의 열이 방열판으로 효과적으로 전달 가능하여 방열구조 4의 방열판 온도가 방열구조 3의 경우보다 높게 나타나는 것으로 판단된다. 따라서, 본 연구를 통해 제한된 공간에서 열전도도가 낮은 PCB에 장착된 고발열체의 방열을 위해 상향 냉각만 고려한 방열구조보다 상하향 냉각을 고려한 방열구조를 채택하는 것이 필요하다고 결론 내릴 수 있다.

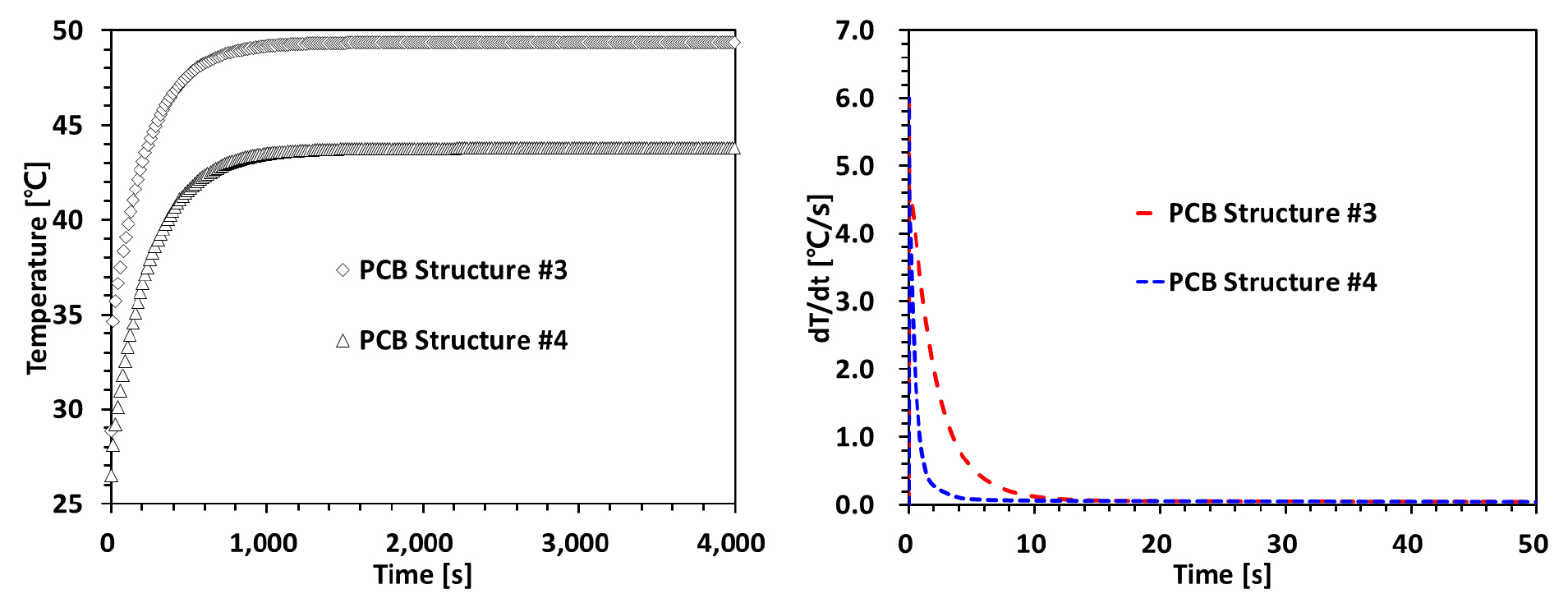

Fig. 7은 방열구조 3과 4의 시간에 따른 GaN-FET의 최대 온도와 최대 온도 변화율을 나타낸 것이다. 두 경우 모두에서 해석 시간이 1,000초에 도달하기 전 GaN-FET의 최대 온도가 안정되는 것을 확인할 수 있다. GaN-FET의 최대 온도는 방열구조 3에서 약 49 ℃이고 방열구조 4에서 약 44 ℃로 나타났다. GaN-FET 하부에 추가로 알루미늄 판을 부착하는 방열구조가 PCB의 크기는 동일하게 하면서 전열면적을 약 22.6% 증가시킬 수 있고 GaN-FET과 알루미늄 판이 직접 접촉하고 있어 방열구조 4의 방열성능이 방열구조 3보다 우수한 것으로 보인다. Fig. 7에서 방열구조 3과 4 모두 해석 시작 후 최대 온도 변화율이 급격히 상승하여 최대 수치인 6 ℃/s에 도달하는 것을 확인할 수 있다. 방열구조 4에서는 GaN-FET의 최대 온도 변화율이 최대 수치 도달 후 방열구조 3의 경우보다 완만히 감소하는 것을 확인할 수 있는데 실제 전력변환장치 운용 시 급격한 발열에 대비하는 측면에서 방열구조 4가 방열구조 3보다 더 유리한 것으로 보인다.

4. 결 론

본 연구에서는 수치해석을 이용하여 3kW급 태양광발전 시스템에 적용할 수 있는 전력변환장치용 GaN-FET의 효과적인 방열을 위해 다양한 방열구조로 이루어진 FR4 소재를 적용한 PCB의 방열특성을 ANSYS Transient-Thermal Analysis 프로그램을 이용하여 분석하였다. 방열구조 1과 2의 해석결과를 통해 바이어 홀을 노출시킨 방열설계는 노출시키지 않은 설계보다 전열면적 측면에서 불리하며, 상대적으로 좁은 열전도 경로를 가져 냉각효율이 상대적으로 떨어지므로 바이어 홀을 노출시키지 않고 방열판에 직접 접촉하는 설계가 GaN-FET에서 발생하는 열의 방열을 위해 바이어 홀을 노출시킨 설계보다 적절한 설계로 분석되었다. 방열구조 3과 4의 해석결과를 통해 상하향 냉각을 고려한 설계가 상향 냉각만 고려한 설계보다 전열면적을 넓게 가져갈 수 있는 장점이 있고, 조립을 위해 적용된 알루미늄 볼트를 통해 열 전도경로를 넓게 형성할 수 있으므로 GaN-FET에서 발생하는 열을 효과적으로 방열하기 위해 상향 냉각보다 상하향 냉각을 채택한 방식이 유리한 것으로 분석되었다. 본 연구결과를 통해 3kW급 태양광발전 시스템에 적용하는 전력변환장치용 GaN-FET의 방열설계를 위한 기초 해석결과를 확보하였으며 이를 토대로 실제 시스템 설계와 제작을 수행 예정이다.